# SARITA ADVE

UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN SADVE@ILLINOIS.EDU

Distribution Statement A. Approved for Public Release

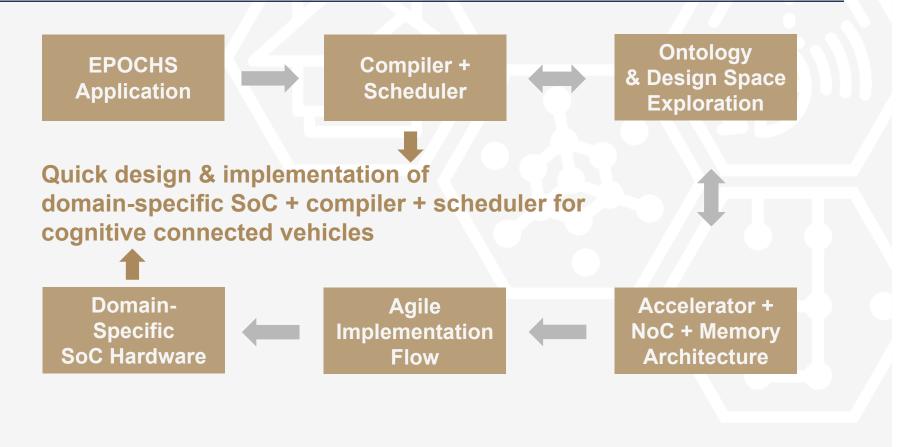

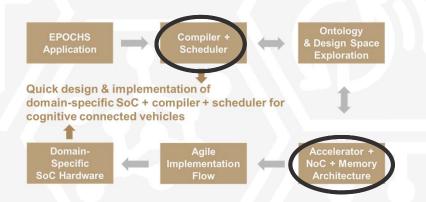

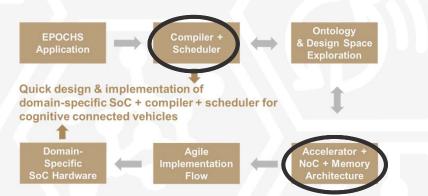

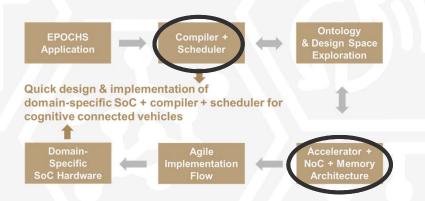

## **EPOCHS OVERVIEW**

S. Adve, V. Adve, P. Bose, D. Brooks, L. Carloni, S. Misailovic, V. Reddi, K. Shepard, G-Y Wei

# **KEY: HARDWARE & SOFTWARE INTERFACES**

Key to heterogeneous system design: Interfaces for hardware & software

- Specializable

- Programmable

- Efficient

#### This talk: Two interfaces

- Spandex: Accelerator communication interface

- Heterogeneous Parallel Virtual Machine (HPVM): Hardware-software interface

Enable specialization with programmability and efficiency

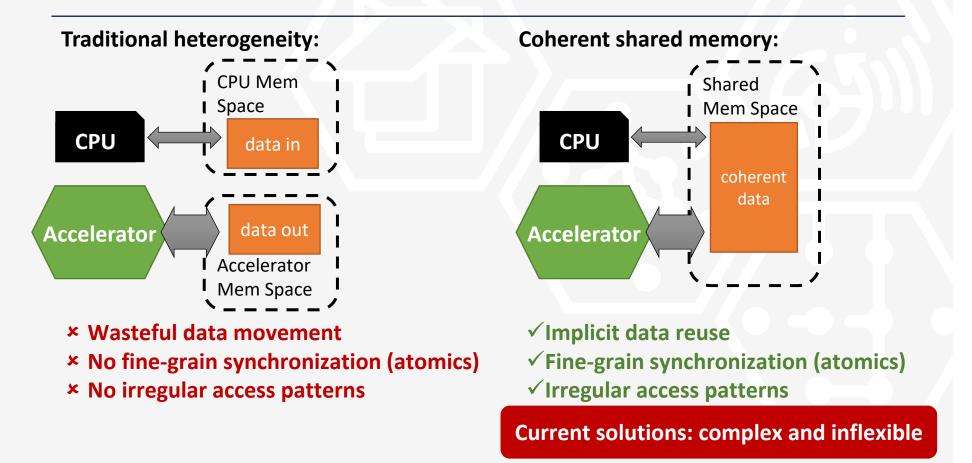

## **HETEROGENEOUS SYSTEMS COMMUNICATION**

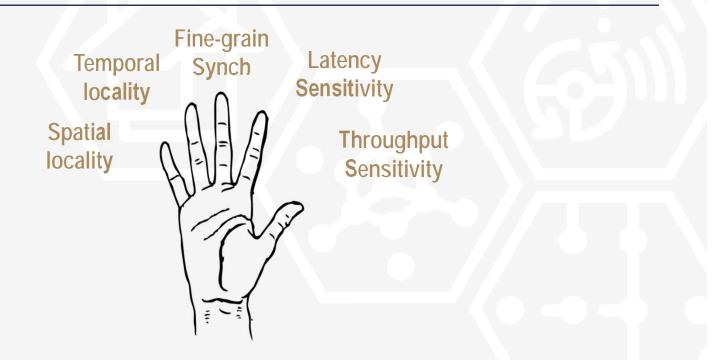

#### HETEROGENEOUS DEVICES HAVE DIVERSE MEMORY DEMANDS

#### HETEROGENEOUS DEVICES HAVE DIVERSE MEMORY DEMANDS

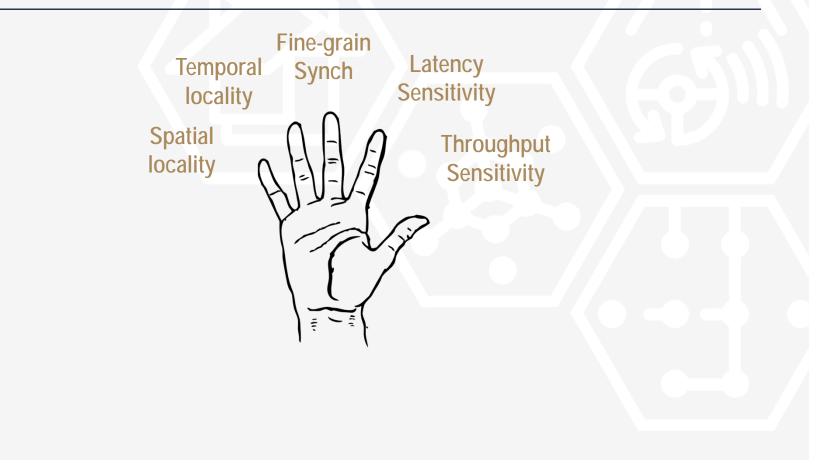

Typical CPU workloads: fine-grain synchronization, latency sensitive

#### HETEROGENEOUS DEVICES HAVE DIVERSE MEMORY DEMANDS

Typical GPU workloads: spatial locality, throughput sensitive

## **KEY PROPERTIES OF COHERENCE PROTOCOLS**

| Properties   |  |

|--------------|--|

|              |  |

| Granularity  |  |

| Invalidation |  |

| Updates      |  |

| I            |  |

## **KEY PROPERTIES OF COHERENCE PROTOCOLS**

| Properties   | CPU MESI          | GPU GPU                     | DeNovo<br>(for CPU or GPU)      |

|--------------|-------------------|-----------------------------|---------------------------------|

| Granularity  | Line              | Reads: Line<br>Writes: Word | Reads: Flexible<br>Writes: Word |

| Invalidation | Writer-invalidate | Self-invalidate             | Self-invalidate                 |

| Updates      | Ownership         | Write-through               | Ownership                       |

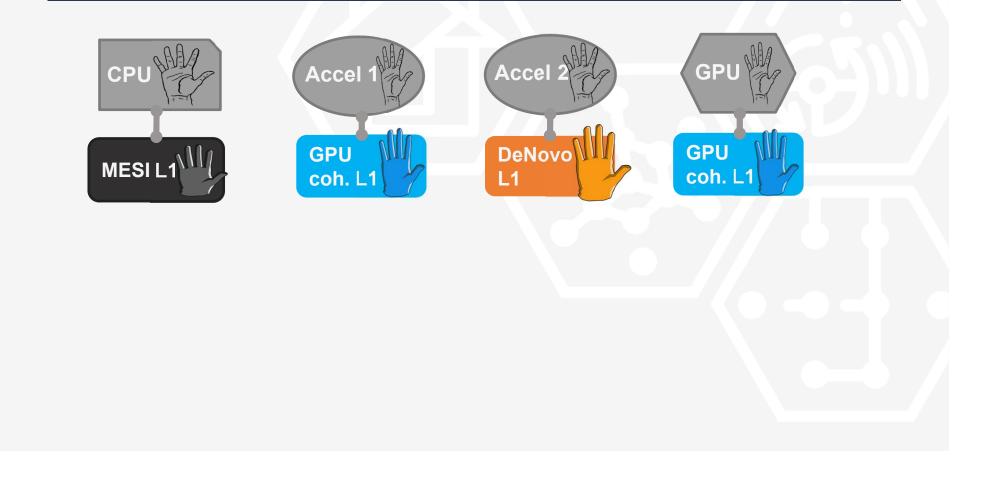

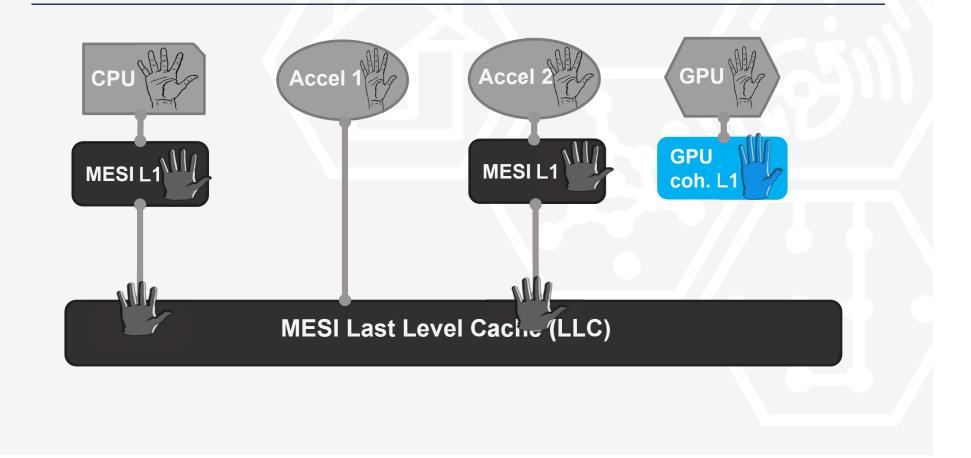

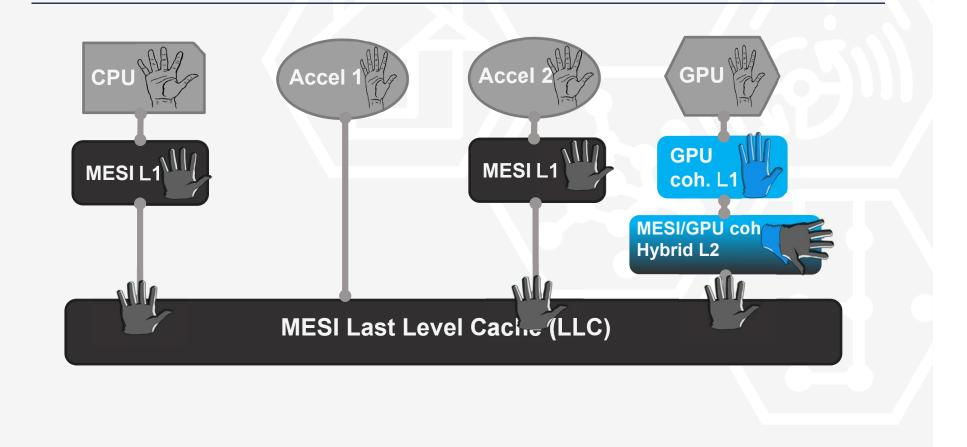

How to integrate different accelerators with different protocols?

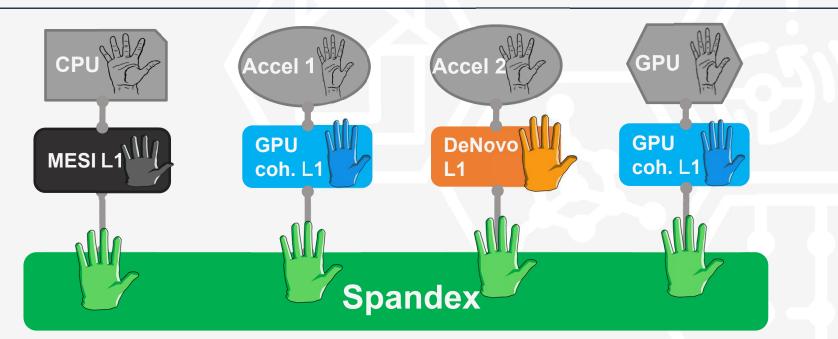

#### SPANDEX: FLEXIBLE HETEROGENEOUS COHERENCE INTERFACE [ISCA'18]

- Adapts to exploit individual device's workload attributes

- Better performance, lower complexity

- $\Rightarrow$  Fits like a glove for heterogeneous systems!

Supported by ADA JUMP and C-FAR STARNET centers

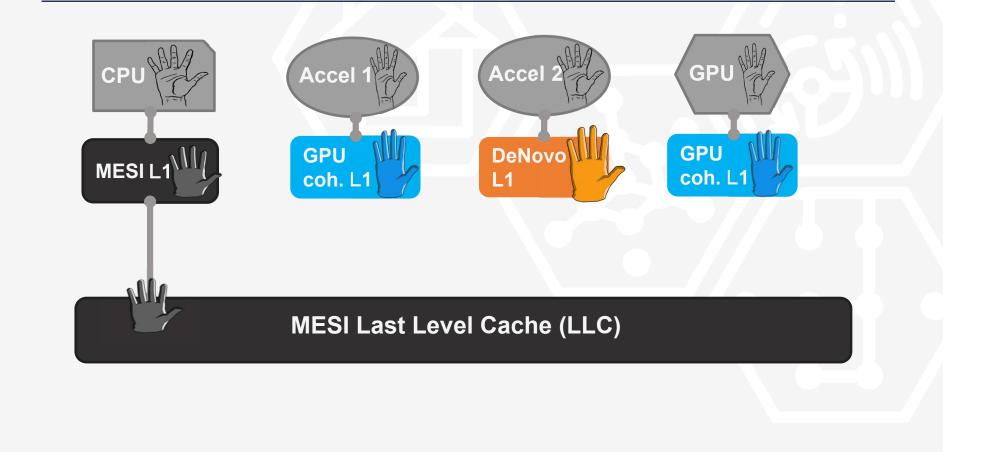

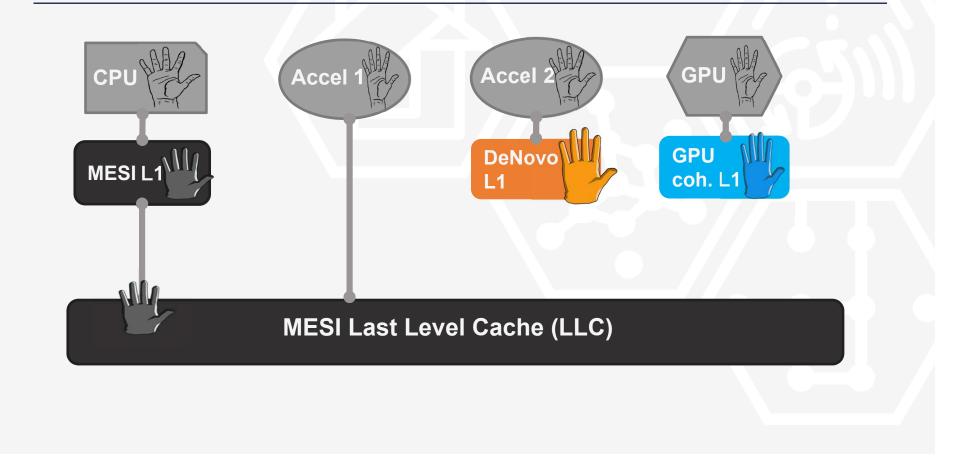

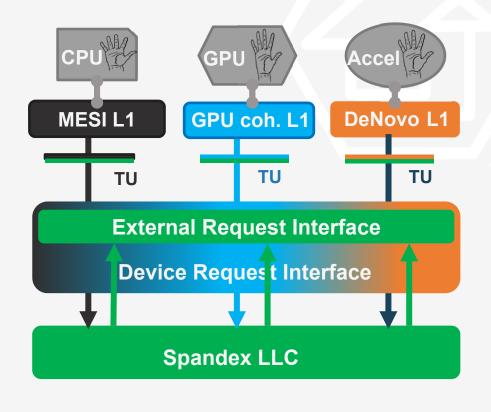

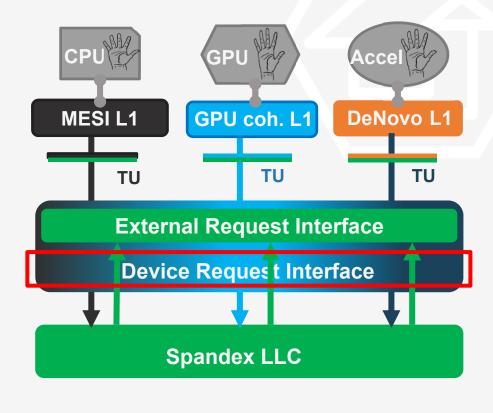

## **SPANDEX OVERVIEW**

#### Key Components

- Flexible device request interface

- DeNovo-based LLC

- External request interface

Device may need a translation unit (TU)

## **SPANDEX OVERVIEW**

#### Key Components

- Flexible device request interface

- DeNovo-based LLC

- External request interface

Device may need a translation unit (TU)

# **SPANDEX DEVICE REQUEST INTERFACE**

| Action    | Request    | Indicates            |

|-----------|------------|----------------------|

| Deed      | ReqV       | Self-invalidation    |

| Read      | ReqS       | Writer-invalidation  |

|           | ReqWT      | Write-through        |

| Write     | ReqO       | Ownership only       |

| Read+     | ReqWT+data | Atomic write-through |

| Write     | ReqO+data  | Ownership + Data     |

| Writeback | ReqWB      | Owned data eviction  |

• Requests also specify granularity and (optionally) a bitmask

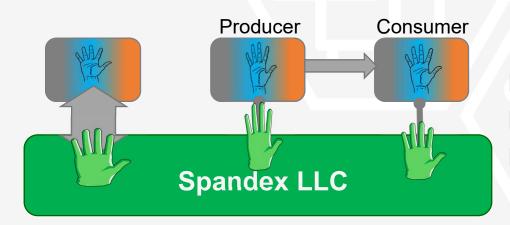

## **DYNAMIC & NEW COHERENCE SPECIALIZATIONS**

• Spandex flexibility & simplicity enables dynamic & new coherence specializations

Dynamic Spandex request selection Producer-consumer forwarding Extended granularity flexibility

- Directed by compiler or runtime

- Applied to neural networks: enables new programming patterns

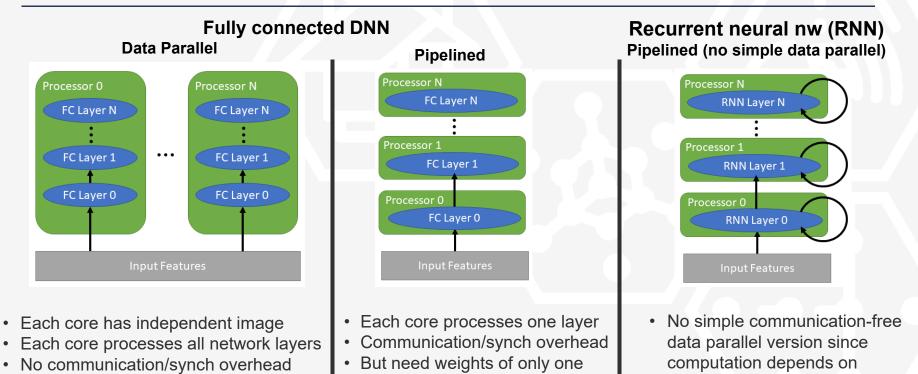

## DATA PARALLEL VS. PIPELINED NEURAL NETWORKS

• But need weights of all layers for reuse layer for reuse

Spandex flexibility enables fine-grained communication and efficient pipelines

previous input

#### COHERENCE SPECIALIZATION FOR PIPELINED NEURAL NETWORKS

- Dynamically select coherence strategy for different data

- Use ownership for weight data (reuse), writethrough for input feature data

#### COHERENCE SPECIALIZATION FOR PIPELINED NEURAL NETWORKS

- Dynamically select coherence strategy for different data

- Use ownership for weight data (reuse), writethrough for input feature data

- Optimization1: Producer  $\rightarrow$  Consumer forward via last level cache (LLC)

- LLC forwards feature output to next consumer

#### COHERENCE SPECIALIZATION FOR PIPELINED NEURAL NETWORKS

- Dynamically select coherence strategy for different data

- Use ownership for weight data (reuse), writethrough for input feature data

- Optimization1: Producer  $\rightarrow$  Consumer forward via last level cache (LLC)

- LLC forwards feature output to next consumer

- Optimization2: Direct Producer → Consumer forward w/ owner prediction

- Producer directly forwards feature data to consumer cache, with no LLC lookup

## **EVALUATION METHODOLOGY**

- Baseline system: CPU + Multiple GPU compute cores on a network on chip

- Neural network (NN) computation on different compute cores of GPUs

- NNs based on standard networks or information from literature

- Cycle accurate architectural simulation: GEMS+GPGPUSim+Garnett+Spandex

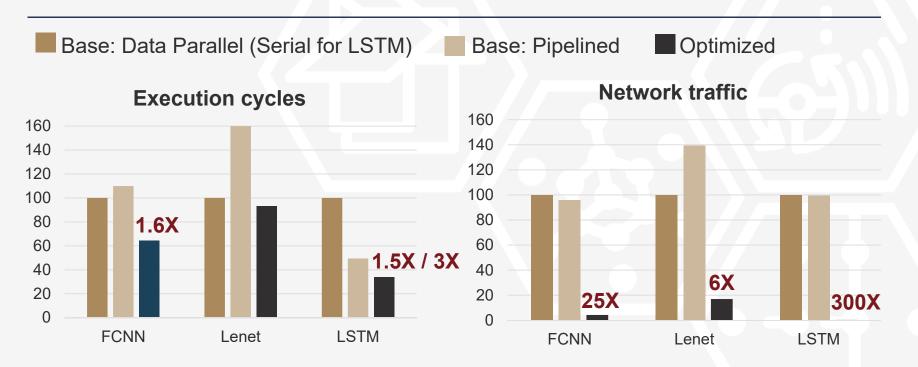

# **RESULTS FOR NEURAL NETWORKS**

Large reduction in execution time and/or network traffic

Next steps for Spandex: Apply to EPOCHS application and integrate with compiler

## **RECAP SO FAR**

Key to heterogeneous system design: Interfaces for hardware & software

- Specializable

- Programmable

- Efficient

#### This talk: Two interfaces

- ✓ Spandex: Accelerator communication interface

- Heterogeneous Parallel Virtual Machine (HPVM): Hardware-software interface

Enable specialization with programmability and efficiency

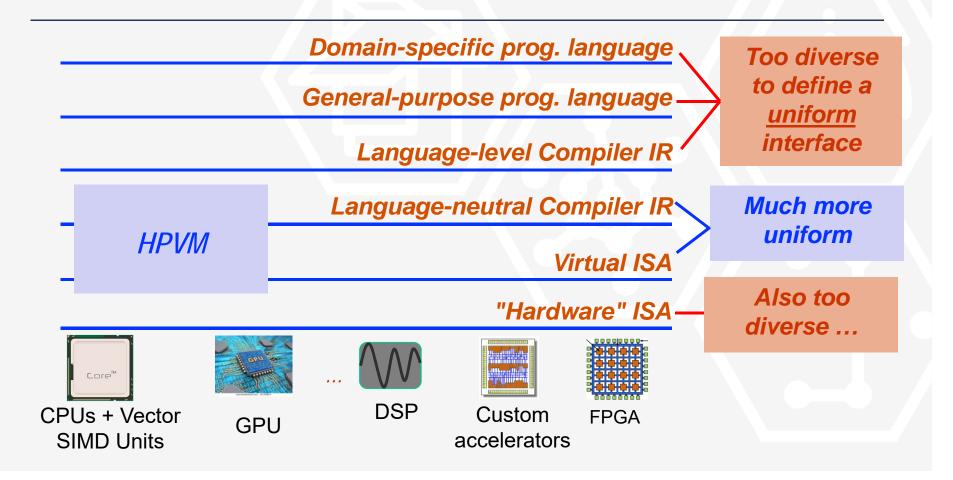

# **CURRENT INTERFACE LEVELS**

| App. productivity                                | Domain-specifi | c prog. language |  |  |  |

|--------------------------------------------------|----------------|------------------|--|--|--|

| App. performance                                 | General-purpos | e prog. language |  |  |  |

| Language innovation Language-level Compiler IR   |                |                  |  |  |  |

| Compiler investment Language-neutral Compiler IR |                |                  |  |  |  |

| Object-code portability Virtual ISA              |                |                  |  |  |  |

| Hardware innovation                              | า              | "Hardware" ISA   |  |  |  |

| Lore™                                            | (\)            |                  |  |  |  |

#### WHERE SHOULD WE ABSTRACT HETEROGENEITY?

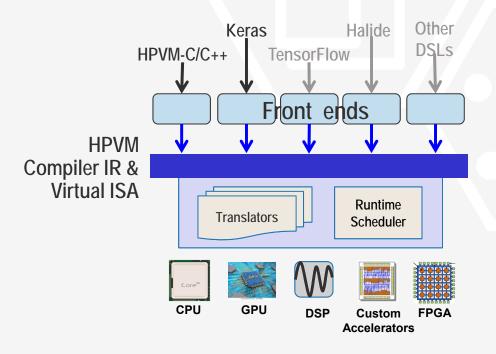

## **HETEROGENEOUS PARALLEL VIRTUAL MACHINE**

## Key to Programmability:

#### Common abstractions for heterogeneous parallel hardware

Use HPVM for:

- 1. Portable object code

- 2. Retargetable parallel compiler IR and system

- 3. Run-time scheduling

Kotsifakou et al., PPOPP 2018

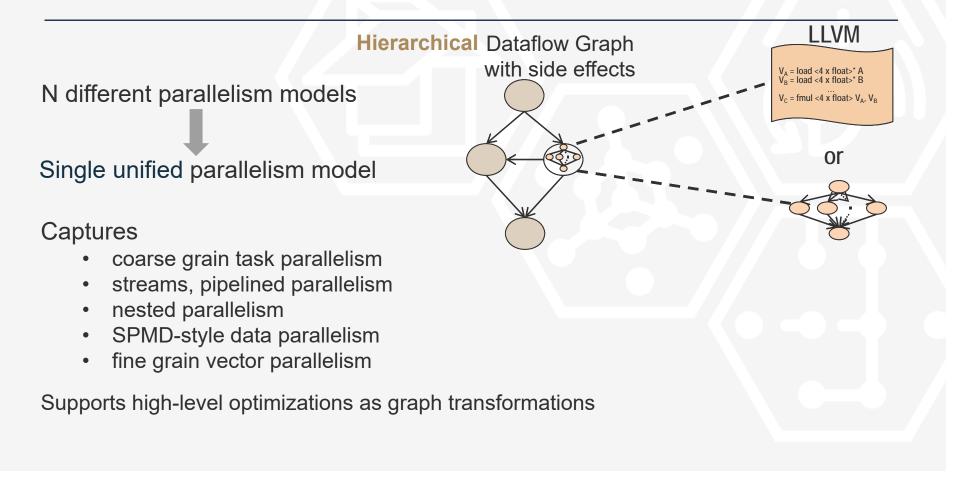

# **ABSTRACTION OF PARALLEL COMPUTATION**

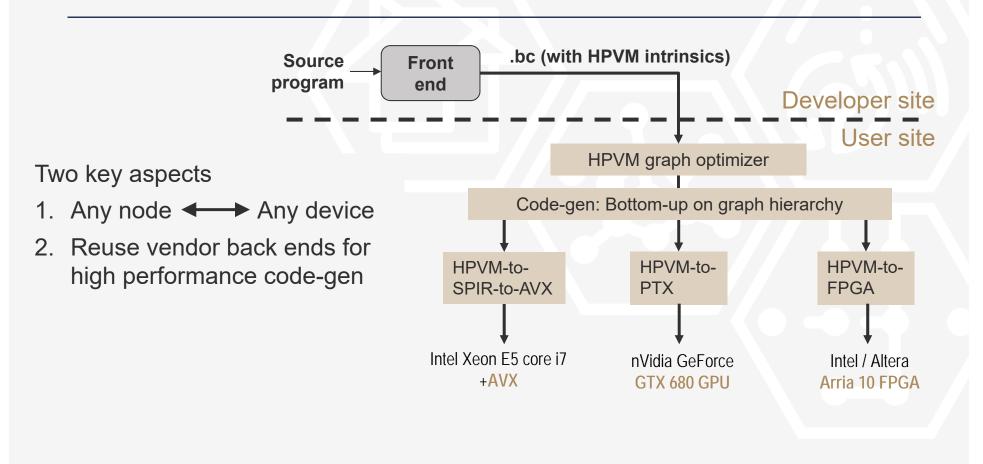

## **HPVM BOTTOM-UP CODE GENERATION**

## **APPROX-HPVM: ACCURACY AWARE OPTIMIZATION**

Relaxing accuracy can enable higher efficiency (2X to 50X in our work) Can we make these techniques easier to use?

Goal 1: Applications should only specify high-level accuracy goals

- Maximum acceptable loss in quality, e.g., inference error, PSNR

- End-to-end metrics, not per function or pipeline stage or …

Goal 2: (Often) Want object-code portability

- Approximation choices are highly system-dependent

- Can make orders-of-magnitude difference in performance, energy

#### ApproxHPVM: Accuracy-aware representation and optimizations Implemented for Keras: Neural networks in TensorFlow

Sharif et al., OOPSLA 2019, accepted with revisions

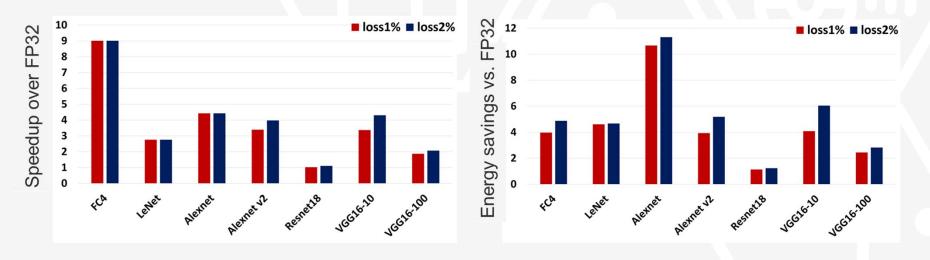

## **DNN SPEEDUP AND ENERGY SAVINGS**

Target system: NVIDIA Tegra TX2 + PROMISE ML accelerator TX2: FP32 or FP16, PROMISE: 7 voltage levels in SRAM bitlines

1-2% loss of inference accuracy gives2X-9X speedup, 2X-11X energy savings in most networks

## **SUMMARY: HARDWARE & SOFTWARE INTERFACES**

Key to heterogeneous system design: Interfaces for hardware & software

- Specializable

- Programmable

- Efficient

#### This talk: Two interfaces

- Spandex: Accelerator communication interface

- Heterogeneous Parallel Virtual Machine (HPVM): Hardware-software interface

Enable specialization with programmability and efficiency

# **ERI** ELECTRONICS RESURGENCE INITIATIVE

# SUMMIT

#### 2019 | DETROIT, MI | JULY 15-17