$\bigodot$  2017 Matthew David Sinclair

#### EFFICIENT COHERENCE AND CONSISTENCY FOR SPECIALIZED MEMORY HIERARCHIES

BY

MATTHEW DAVID SINCLAIR

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2017

Urbana, Illinois

Doctoral Committee:

Professor Sarita V. Adve, Chair & Director of Research Professor Vikram S. Adve Professor Todd Austin, University of Michigan Dr. Bradford Beckmann, AMD Research Professor David Brooks, Harvard University Professor Rob A. Rutenbar Professor Marc Snir

### Abstract

As the benefits from transistor scaling slow down, specialization is becoming increasingly important for a wide range of applications. Although traditional heterogeneous systems work well for streaming, data parallel applications, they are inefficient for emerging applications, like graph analytics workloads, with fine-grained synchronization, relaxed atomics, and more general sharing patterns. Heterogeneous systems are also difficult to program, which makes it harder for programmers to take advantage of the potential benefits of specialization.

This thesis redesigns the memory hierarchy of heterogeneous systems to make heterogeneous systems more efficient and easier to use. In particular, we focus on three key sources of inefficiency in the memory hierarchy of modern heterogeneous systems: (1) a unified global address space, (2) the cache coherence protocol, and (3) the memory consistency model.

A unified global address space makes it easier to write programs for heterogeneous systems. Although industry has recently begun to provide a unified global address space across CPUs and accelerators (primarily GPUs), there are many inefficiencies. For example, emerging applications with fine-grained synchronization need better support for coherence and consistency. We find that simple coherence and complex consistency are key sources of inefficiency. To resolve this problem, we adjust the division of complexity between the cache coherence protocol and memory consistency model: we introduce DeNovo for accelerators (DeNovoA), which extends DeNovo's hybrid, softwaredriven hardware coherence protocol to heterogeneous systems. Unlike current coherence protocols for heterogeneous systems, DeNovoA obtains ownership for written data, enables heterogeneous systems to use the simpler sequentially consistent for data-race-free (SC-for-DRF, or DRF) memory consistency model, and provides both efficiency and programmability. Across a wide variety of applications, DeNovoA with a DRF memory consistency model either outperforms or provides comparable efficiency to a the state-of-the-art approach. Although DRF is easier to use and works well for most applications, there are some corner cases where its overheads are unnecessary and hurt performance. This led to the introduction of relaxed atomics in the memory consistency models for multi-core CPUs and heterogeneous systems. Although relaxed atomics can significantly improve performance, they are very difficult to use correctly. We address the impact of relaxed atomics on memory consistency models for heterogeneous systems by creating a new memory consistency model, *Data-Race-Free-Relaxed* or *DRFrlx*. DRFrlx extends the existing DRF memory consistency models to provide SC-centric semantics for all common uses of relaxed atomics in heterogeneous systems *while* retaining their efficiency benefits. Thus, DRFrlx makes it easier for programmers to safely use relaxed atomics.

Although current heterogeneous systems are adopting unified global address spaces, specialized memories such as scratchpads still exist in disjoint, private address spaces. This increases programming complexity and causes inefficiencies that negate some of the benefits of specialization. We introduce a new memory organization, *stash*, that mitigates the inefficiencies of specialized memories by integrating them into the coherent, globally visible address space. Stash makes it easier for programmers to use specialized memories and retains their efficiency benefits.

Finally, to better understand the tradeoffs and scalability of different coherence protocols and consistency models, we created a suite of synchronization microbenchmarks, HeteroSync. HeteroSync contains various fine-grained synchronization and relaxed atomics algorithms. Moreover, HeteroSync is highly configurable and provides a standard set of fine-grained synchronization microbenchmarks to compare the efficiency of different approaches.

In summary, this thesis questions the state-of-the-art approaches for designing memory hierarchies of heterogeneous systems, and shows that the current techniques provide neither efficiency nor programmability for emerging workloads. We demonstrate how DeNovoA with a DRFrlx memory consistency model improves efficiency and programmability for many heterogeneous applications and makes it easier for programmers to use heterogeneous systems. To my Dad, who isn't around to see this day. I know you're looking down on me and smiling. To my Mom, for always supporting me. To Ann, for her constant encouragement.

### Acknowledgments

I owe a debt of gratitude to a number of people who have helped me along the way. Most of all, I need to thank my advisor, Sarita Adve, for all of her help along the way. Working with Sarita has been a wonderful experience, and I am a better researcher and person for having worked with her. Her drive, patience, and commitment to excellence are inspiring, and things I strive to emulate moving forward.

Vikram Adve has also provided me with much sage advice along the way. No matter how busy he was, Vikram always had time to listen to my questions and offer constructive feedback. Similarly, despite their very busy schedules, Rob Rutenbar and Marc Snir always made me feel welcome and offered input from a different perspective that challenged me and made me think more critically about my work.

I also sincerely appreciate the input and feedback from the rest of my Ph.D. committee, Todd Austin, Brad Beckmann, and David Brooks, which significantly improved the quality of my work. Special thanks as well to Brad, Pablo Montesinos, Mike O'Connor, and Steve Keckler, among others, who exposed me to real world problems for heterogeneous systems.

Sarita's research group is full of wonderful, talented, and kind students. Working with them has been a wonderful experience for me and helped me grow in many different facets. I am especially thankful to Rakesh Komuravelli and Hyojin Sung for their collaboration and guidance during the stash project, Siva Hari for his kind, patient mentoring, and John Alsop for all of his help with the scopes, relaxed atomics, and HeteroSync projects. Additionally, I am thankful to my other collaborators and/or lab-mates: Khalique Ahmed, Lin Cheng, Byn Choi, Adel Ejjeh, Muhammad Huzaifa, Maria Kotsifakou, Abdulrahman Mahmoud, Sean Nicolay, Giordano Salvador, Rob Smolinski, Prakalp Srivastava, and Radha Venkatagiri.

The staff in the Computer Science department at Illinois is top notch, and they have also

helped me significantly along the way. Special thanks to Rhonda McElroy, both for her help in the department and with the Mavis Future Faculty Fellows program, and Colin Robertson, for all of his help with the fellowships and awards. Similarly, I am indebted to Dana Garard, Molly Flesner, Joe Jeffries, Michelle Osbourne, Meg Osfar, Tierra Reed, and Sherry Unkraut, not just for their help in completing various administrative tasks, but also for the interesting conversations and discussions. Finally, thanks to Julie Gustafson, Erin Henkelman, Mary Beth Kelley, Viveka Kudaligama, Kara MacGregor, and Kathy Ann Runck for making it easy for me to succeed.

Many, many thank yous to the TSG/Engineering IT staff for all of their patient help along the way, especially to Palmer Buss, Joel Franzen, Glen Rundblom, and Vincent Weathers. Without their help, none of the equipment I relied on daily would have worked properly.

My work has been supported by Intel through the Illinois/Intel Parallelism Center at Illinois, by the National Science Foundation under grants CCF 10-18796, CCF 13-02641, and CCF 16-19245 and by the Center for Future Architectures Research (C-FAR), one of six centers of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA. My work was also supported by a Qualcomm Innovation Fellowship. Extra special thanks to Dr. Matsushita, Mrs. Poppelbaum, and Dr. and Mrs. Mavis for endowing the Saburo Muroga Fellowship, C.W. Poppelbaum Award, and Mavis Future Faculty Fellowship, respectively. I am honored to have been a recipient of these awards and fellowships.

Along the way I was lucky enough to meet a great group of people in Urbana-Champaign, who enriched my life significantly. A special thanks to Robert Deloatch and Ryan Musa for their friendship. Similarly, I am grateful to Henry Duwe, both for his friendship and for his sage advice.

I am also grateful to my family for providing support and encouragement along the way. I am very lucky to have grown up in a nurturing environment where learning was encouraged. Finally, thanks to my wife Ann. Without you, I would never have succeeded: whenever I was tired you were there for me. I proudly dedicate this thesis to you.

### **Table of Contents**

| List of | f Tables                                                           | x   |

|---------|--------------------------------------------------------------------|-----|

| List of | f Figures                                                          | xi  |

| List of | f Abbreviations                                                    | xii |

| Chapte  | er 1 Introduction                                                  | 1   |

| 1.1     | Motivation                                                         | 1   |

| 1.2     | Summary of Contributions                                           | 5   |

| 1.3     | Long-Term Impact                                                   | 7   |

| 1.4     | Thesis Organization                                                | 9   |

| Chapte  | er 2 Efficient Coherence and Consistency for Heterogeneous Systems | 10  |

| 2.1     | Motivation                                                         | 10  |

| 2.2     | Background                                                         | 12  |

|         | 2.2.1 GPU Coherence                                                | 12  |

|         | 2.2.2 Memory Consistency Models                                    | 13  |

| 2.3     | A Classification of Coherence Protocols                            | 14  |

| 2.4     | Qualitative Analysis of the Protocols                              | 18  |

|         | 2.4.1 Qualitative Performance Analysis                             | 18  |

|         | 2.4.2 Protocol Implementation Overheads                            | 20  |

| 2.5     | Methodology                                                        | 21  |

|         | 2.5.1 Baseline Heterogeneous Architecture                          | 21  |

|         | 2.5.2 Simulation Environment and Parameters                        | 23  |

|         | 2.5.3 Protocol Extensions and Assumptions                          | 23  |

|         | 2.5.4 Configurations                                               | 25  |

|         | 2.5.5 Benchmarks                                                   | 26  |

| 2.6     | Synchronization Primitive Microbenchmarks                          | 28  |

|         | 2.6.1 Mutexes                                                      | 30  |

|         | 2.6.2 Semaphores                                                   | 32  |

|         | 2.6.3 Barriers                                                     | 35  |

| 2.7     | Results                                                            | 37  |

|         | 2.7.1 GD vs. GH                                                    | 40  |

|         | 2.7.2 DD vs. GPU Coherence                                         | 41  |

|         | 2.7.3 DD with Selective (RO) Invalidations                         | 44  |

|         | 2.7.4 Applying HRF to DeNovoA                                      | 45  |

| 2.8     | Summary                                                            | 45  |

| Chapte     | er 3 Efficient Support for and Evaluation of Relaxed Atomics         | <b>48</b> |

|------------|----------------------------------------------------------------------|-----------|

| 3.1        | Motivation                                                           | 48        |

|            | 3.1.1 Current Semantics with Relaxed Atomics                         | 50        |

|            | 3.1.2 Approach for Semantics                                         | 51        |

| 3.2        | Background: DRF1 Consistency Model                                   | 53        |

|            | 3.2.1 Terminology                                                    | 54        |

|            | 3.2.2 DRF1 Formal Definition                                         | 54        |

| 3.3        | Relaxed Atomic Use Cases and DRFRlx Model                            | 55        |

|            | 3.3.1 Unpaired Atomics                                               | 56        |

|            | 3.3.2 Commutative Atomics                                            | 57        |

|            | 3.3.3 Non-Ordering Atomics                                           | 59        |

|            | 3.3.4 Speculative Atomics                                            | 62        |

|            | 3.3.5 Quantum Atomics                                                | 65        |

|            | 3.3.6 Distinguishing Memory Operations                               | 69        |

|            | 3.3.7 DRFrlx Systems                                                 | 70        |

|            | 3.3.8 Mechanizing DRFrlx                                             | 70        |

| 3.4        | Qualitative Analysis                                                 | 70<br>73  |

| 3.4<br>3.5 | Methodology                                                          | 73<br>74  |

| 5.0        |                                                                      |           |

|            | 3.5.1 Configurations                                                 | 74        |

| 9.6        | 3.5.2 Benchmarks                                                     | 74<br>72  |

| 3.6        | Results                                                              | 76<br>70  |

|            | 3.6.1 Varying Number of Histogram Bins                               | 78        |

|            | 3.6.2 DRF0 vs. DRF1                                                  | 80        |

|            | 3.6.3 DRF1 vs. DRFrlx                                                | 81        |

|            | 3.6.4 DeNovoA vs. GPU Coherence                                      | 82        |

| 3.7        | Summary                                                              | 83        |

| Chapte     | er 4 Integrating Specialized Memories Into the Unified Address Space | 85        |

| 4.1        | Motivation                                                           | 85        |

| 4.2        | Background: Memory Organizations                                     | 86        |

| 4.2        | 4.2.1 Cache                                                          | 87        |

|            | 4.2.1 Cache                                                          |           |

|            |                                                                      |           |

| 4.9        | 1 0                                                                  |           |

|            | Stash Overview                                                       |           |

| 4.4        | Stash Software Interface                                             | 91<br>01  |

|            | 4.4.1 Specifying Stash-to-Global Mapping                             | 91        |

|            | 4.4.2 Stash Load and Store Instructions                              | 92        |

|            | 4.4.3 Usage Modes                                                    | 92        |

| 4.5        | Stash Hardware Design                                                | 93        |

|            | 4.5.1 Stash Components                                               | 94        |

|            | 4.5.2 Operations                                                     | 95        |

|            | 4.5.3 Address Translation                                            | 98        |

|            | 4.5.4 Coherence Protocol Extensions for Stash                        | 99        |

|            | 4.5.5 State Bits Overhead for Stash Storage                          | .02       |

|            | 4.5.6 Stash Optimization: Data Replication                           | .02       |

| 4.6        | Methodology                                                          |           |

|            | 4.6.1 Simulated Memory Configurations                                | .03       |

|         | 4.6.2Conveying Information from Application104.6.3Workloads10                                                                                               |           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 4.7     | Results                                                                                                                                                     |           |

| 1.1     | 4.7.1 Access Energy Comparisons                                                                                                                             |           |

|         | 4.7.2 Microbenchmarks                                                                                                                                       |           |

|         | 4.7.3 Applications                                                                                                                                          |           |

| 4.8     | Summary                                                                                                                                                     |           |

|         |                                                                                                                                                             |           |

| Chapte  |                                                                                                                                                             |           |

| 5.1     | Motivation                                                                                                                                                  |           |

| 5.2     | Methodology                                                                                                                                                 |           |

|         | 5.2.1 Configurations $\ldots \ldots \ldots$ |           |

|         | 5.2.2 Benchmarks                                                                                                                                            |           |

| 5.3     | Results                                                                                                                                                     |           |

|         | 5.3.1 Local/Hybrid SyncPrims                                                                                                                                |           |

|         | 5.3.2 Global SyncPrims                                                                                                                                      |           |

| - 1     | 5.3.3 Relaxed Atomics                                                                                                                                       |           |

| 5.4     | Summary                                                                                                                                                     | 1         |

| Chapte  | er 6 Related Work                                                                                                                                           | <b>2</b>  |

| 6.1     | Coherence & Consistency for Heterogeneous Systems                                                                                                           |           |

|         | 6.1.1 Memory Consistency Models                                                                                                                             | <b>52</b> |

|         | 6.1.2 Coherence Protocols                                                                                                                                   | 33        |

|         | 6.1.3 Subsequent Coherence Protocols                                                                                                                        | 54        |

| 6.2     | Relaxed Atomics                                                                                                                                             | 55        |

|         | 6.2.1 Memory Consistency Models                                                                                                                             | 55        |

|         | 6.2.2 Memory Orderings                                                                                                                                      | <b>57</b> |

|         | 6.2.3 Other Related Work                                                                                                                                    | <b>57</b> |

| 6.3     | Private Memories                                                                                                                                            | 8         |

| 6.4     | Synchronization Benchmarks                                                                                                                                  | 0         |

| Chapte  | er 7 Conclusions and Future Directions                                                                                                                      | .1        |

| 7.1     | Conclusions                                                                                                                                                 |           |

| 7.2     | Future Directions                                                                                                                                           |           |

|         | 7.2.1 Coherence                                                                                                                                             |           |

|         | 7.2.2 Consistency                                                                                                                                           |           |

|         | 7.2.3 Specialized Memories                                                                                                                                  |           |

|         |                                                                                                                                                             |           |

| Bibliog | ${ m graphy}$                                                                                                                                               | 7         |

## List of Tables

| 2.1               | Classification of protocols covering conventional HW (e.g., MESI), Software (e.g., GPU), and Hybrid (e.g., DeNovoA) coherence protocols                                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2               | Comparison of studied coherence protocols                                                                                                                                                                                                             |

| 2.2<br>2.3        | Simulated heterogeneous system parameters.                                                                                                                                                                                                            |

| 2.4               | Benchmarks with input sizes. All thread blocks (TBs) in the synchronization mi-<br>crobenchmarks execute the critical section or barrier many times. Microbenchmarks<br>with local and global scope are denoted with a '_L' and '_G', respectively 26 |

| 2.5               | Synchronization primitive microbenchmarks                                                                                                                                                                                                             |

| 3.1<br>3.2<br>3.3 | GPU relaxed atomic use cases.       58         Benefits of DRF0, DRF1, and DRFrlx.       73         Benchmarks, input sizes, and relaxed atomics used.       75                                                                                       |

| 4.1<br>4.2        | Comparison of cache, scratchpad, and stash                                                                                                                                                                                                            |

|                   | the index)                                                                                                                                                                                                                                            |

| 4.3               | Stash-specific parameters of the simulated heterogeneous system                                                                                                                                                                                       |

| 4.4               | Input sizes and stash usage modes of applications                                                                                                                                                                                                     |

| 4.5               | Per access energy for various hardware units                                                                                                                                                                                                          |

| 5.1               | SyncPrims microbenchmarks with input sizes used for scaling study. The version of each microbenchmark with local and global scope are again denoted with a 'L' and                                                                                    |

| -                 | '_G', respectively                                                                                                                                                                                                                                    |

| 5.2               | Relaxed atomic microbenchmarks with input sizes used for scaling study 123                                                                                                                                                                            |

| 6.1               | Comparison of DeNovoA to other GPU coherence schemes. The read-only region<br>enhancement to DeNovoA also allows valid data reuse for read-only data                                                                                                  |

| 6.2               | Comparison of stash and prior work                                                                                                                                                                                                                    |

|                   |                                                                                                                                                                                                                                                       |

# List of Figures

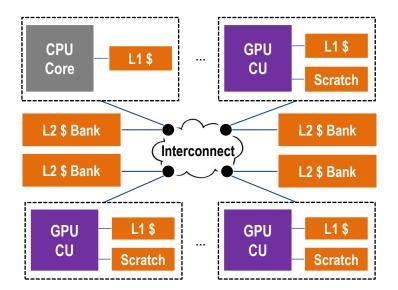

| 2.1 | Baseline heterogeneous architecture                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

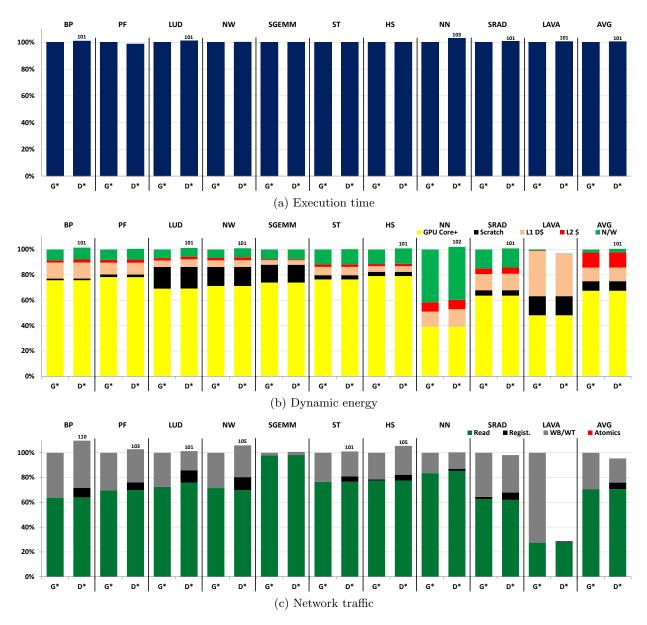

| 2.2 | $G^*$ and $D^*$ , normalized to $D^*$ , for benchmarks without synchronization                                                                                            |

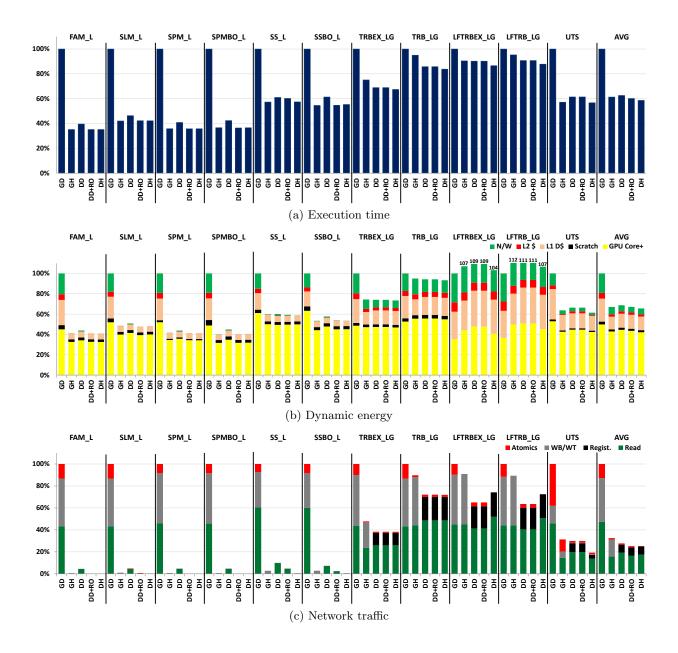

| 2.3 | All configurations with synchronization benchmarks that use mostly local synchro-                                                                                         |

|     | nization, normalized to $GD$                                                                                                                                              |

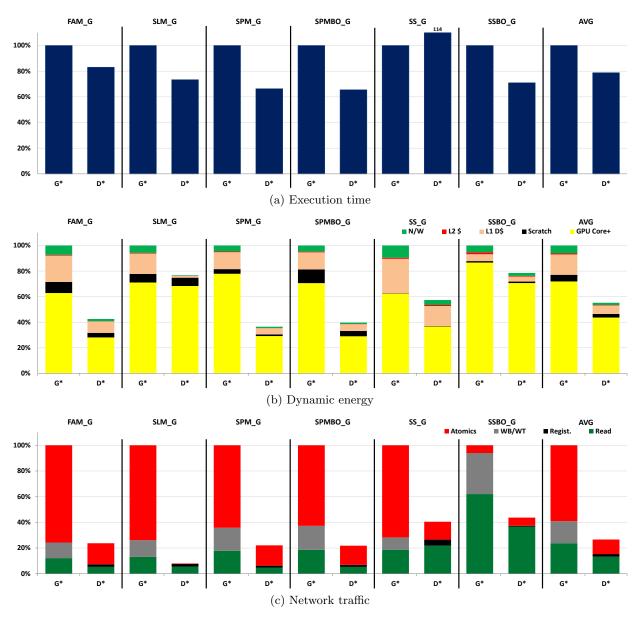

| 2.4 | $G^*$ and $D^*$ , normalized to $G^*$ , for globally scoped synchronization benchmarks 42                                                                                 |

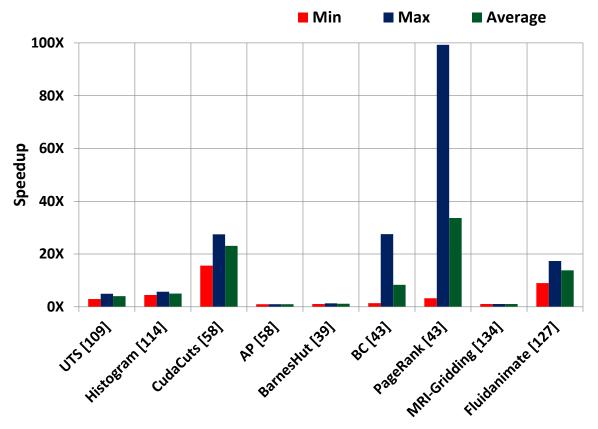

| 3.1 | Relaxed atomics speedup on a discrete GPU                                                                                                                                 |

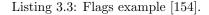

| 3.2 | Executions with program/conflict graphs and ordering paths, (a) with a non-ordering race and (b) without a non-ordering race. UNP = unpaired, NO = non-ordering, P        |

|     | $= paired.  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                              |

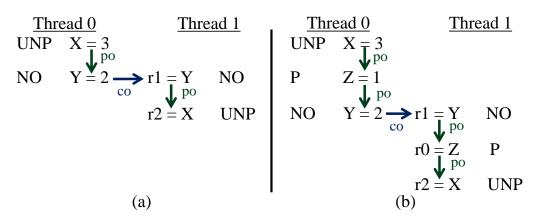

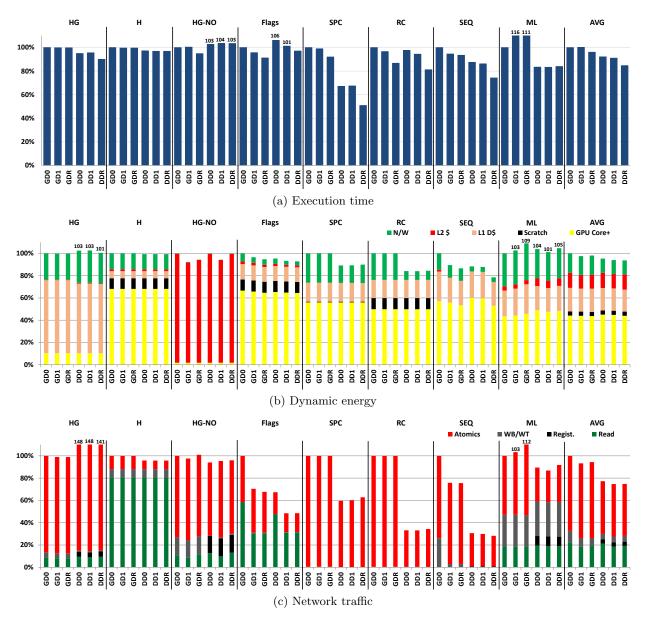

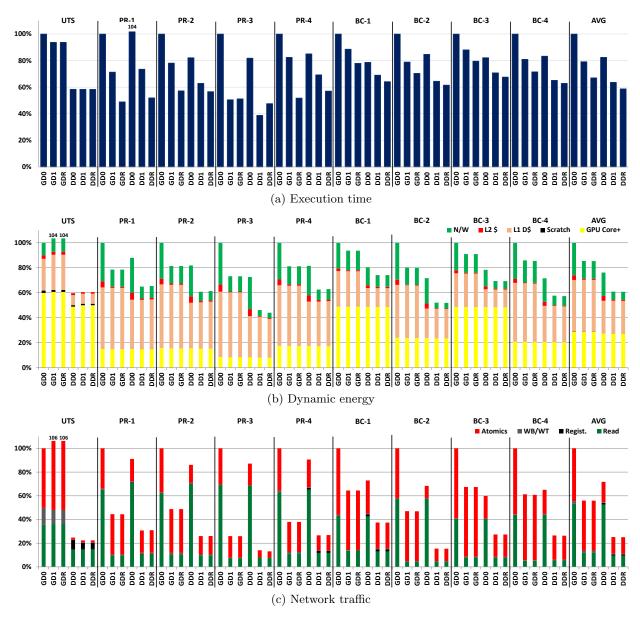

| 3.3 | Results for all microbenchmarks, normalized to GD0                                                                                                                        |

| 3.4 | Results for all benchmarks, normalized to $GD0$                                                                                                                           |

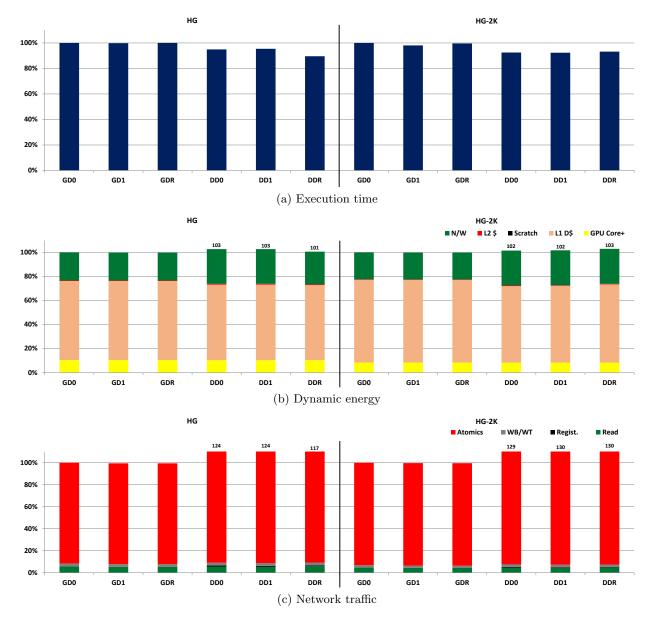

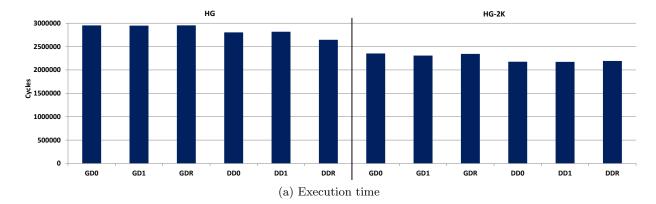

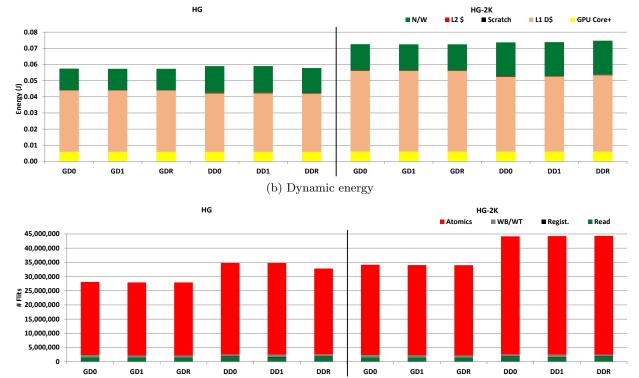

| 3.5 | Results for varying number of histogram bins, normalized to GD0                                                                                                           |

| 3.6 | Absolute results for varying number of histogram bins                                                                                                                     |

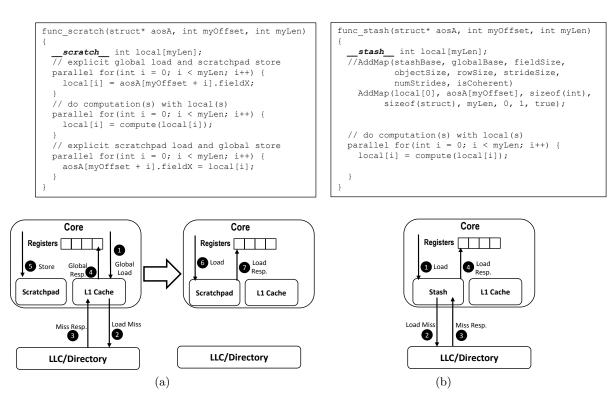

| 4.1 | Codes and hardware events to copy data from the corresponding global address for<br>(a) scratchpad and (b) stash (events to write data back to the global address are not |

|     | shown). $\ldots$                                                                         |

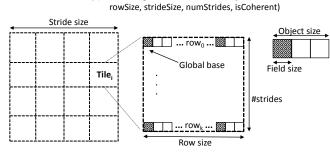

| 4.2 | Mapping a global 2D AoS tile to a 1D stash address space                                                                                                                  |

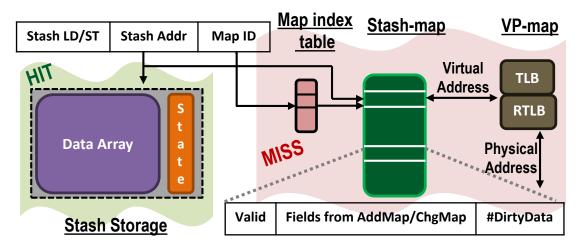

| 4.3 | Stash hardware components                                                                                                                                                 |

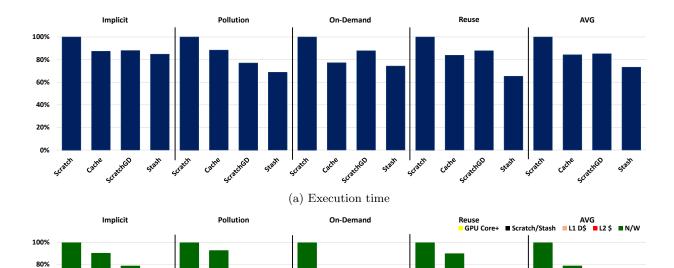

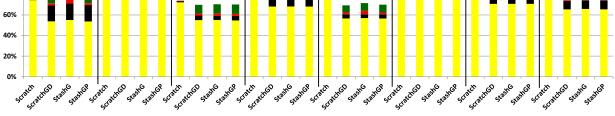

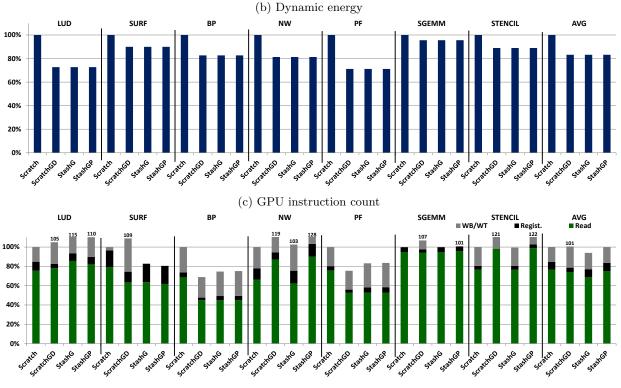

| 4.4 | Comparison of microbenchmarks. The bars are normalized to the <i>Scratch</i> configu-                                                                                     |

|     | ration                                                                                                                                                                    |

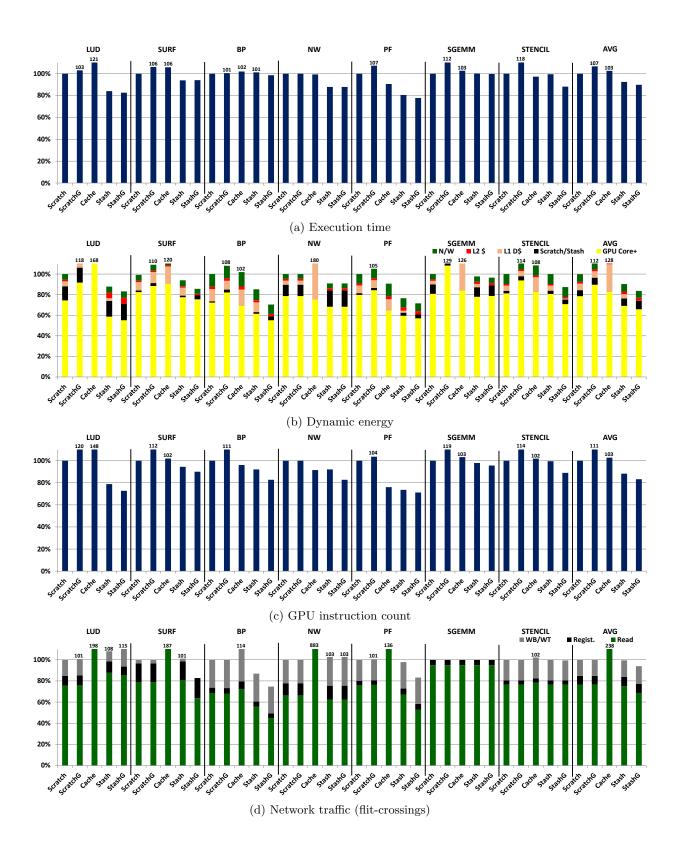

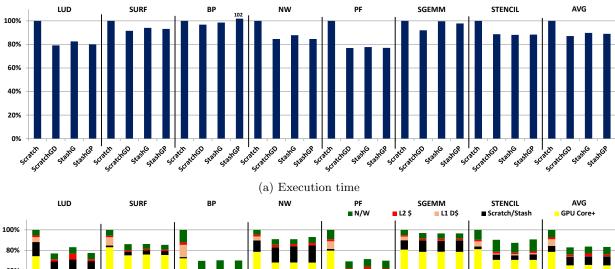

| 4.5 | Comparison of configurations for the seven benchmarks. The bars are normalized to                                                                                         |

|     | the <i>Scratch</i> configuration                                                                                                                                          |

| 4.6 | Comparison of the prefetching configurations for the seven benchmarks, normalized                                                                                         |

|     | to <i>Scratch</i>                                                                                                                                                         |

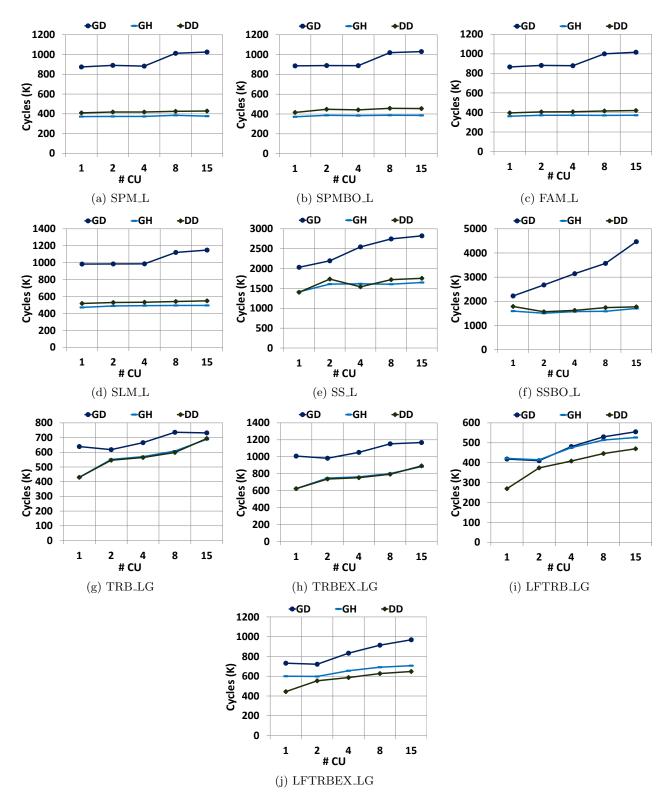

| 5.1 | Weak scaling results for local and hybrid scoped synchronization benchmarks $126$                                                                                         |

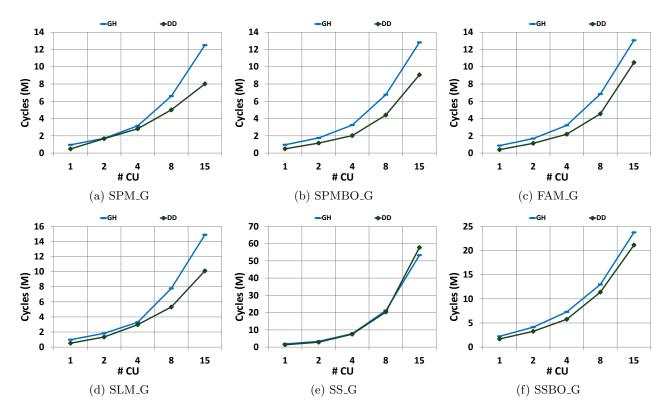

| 5.2 | Weak scaling results for globally scoped synchronization benchmarks                                                                                                       |

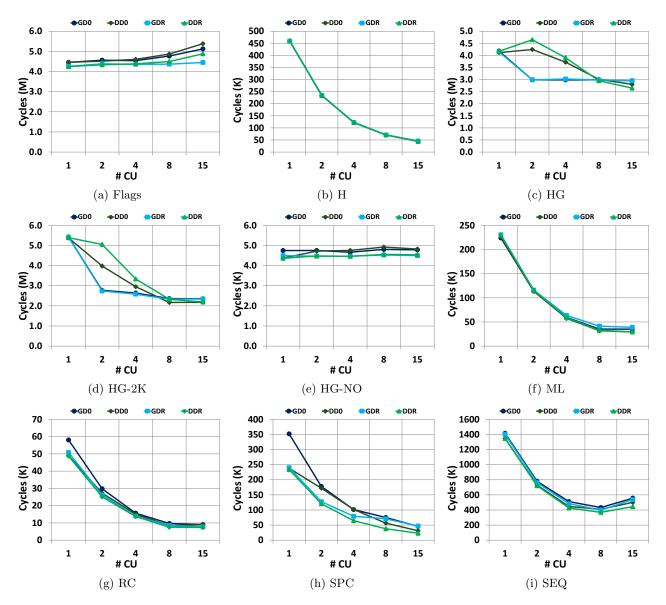

| 5.3 | Strong scaling results for relaxed atomic benchmarks                                                                                                                      |

## List of Abbreviations

| AoS     | Array of Structures                                                                                     |

|---------|---------------------------------------------------------------------------------------------------------|

| BC      | Betweenness Centrality                                                                                  |

| BP      | Backprop                                                                                                |

| CU      | Compute Unit                                                                                            |

| DeNovoA | DeNovo for Accelerators                                                                                 |

| DD      | DeNovoA coherence, DRF consistency                                                                      |

| DD0     | DeNovoA coherence, DRF0 consistency                                                                     |

| DD1     | DeNovoA coherence, DRF1 consistency                                                                     |

| DDR     | DeNovoA coherence, DRFRlx consistency                                                                   |

| DD+RO   | DD with read-only optimization                                                                          |

| DH      | DeNovoA coherence, DRF consistency                                                                      |

| DMA     | Direct Memory Access                                                                                    |

| FAM     | Fetch-and-Add Mutex                                                                                     |

| GD      | GPU coherence, DRF consistency                                                                          |

| GD0     | GPU coherence, DRF0 consistency                                                                         |

| GD1     | GPU coherence, DRF1 consistency                                                                         |

| GDR     | GPU coherence, DRFrlx consistency                                                                       |

| GH      | GPU coherence, HRF consistency                                                                          |

| GPGPU   | General-purpose GPU                                                                                     |

| GPU     | Graphics Processing Unit                                                                                |

| GSI     | GPU Stall Inspector                                                                                     |

| Н       | Histogram                                                                                               |

|         | BC<br>BP<br>CU<br>DeNovoA<br>DD<br>DD<br>DD<br>DD<br>DD<br>DD<br>DD<br>CD<br>CD<br>CD<br>CD<br>CD<br>CD |

| HG                                          | Histogram Global                                   |  |  |  |  |

|---------------------------------------------|----------------------------------------------------|--|--|--|--|

| HG-2K                                       | Histogram Global with 2K bins                      |  |  |  |  |

| HG-NO                                       | Histogram Global-Non-Ordering                      |  |  |  |  |

| hLRC heterogeneous Lazy Release Consistency |                                                    |  |  |  |  |

| HSA                                         | Heterogeneous System Architecture                  |  |  |  |  |

| hVISC                                       | heterogeneous Virtual Instruction Set Computing    |  |  |  |  |

| HW                                          | Hardware                                           |  |  |  |  |

| Lava                                        | LavaMD                                             |  |  |  |  |

| LFTRB                                       | Lock-Free Tree Barrier                             |  |  |  |  |

| LFTRBEX                                     | Lock-Free Tree Barrier with local data exchange    |  |  |  |  |

| LLC                                         | Last Level Cache                                   |  |  |  |  |

| LUD                                         | LU Decomposition                                   |  |  |  |  |

| ML                                          | Multiple Locks                                     |  |  |  |  |

| NN                                          | Nearest Neighbor                                   |  |  |  |  |

| NW                                          | Needlman-Wunsch                                    |  |  |  |  |

| PF                                          | Pathfinder                                         |  |  |  |  |

| PR                                          | PageRank                                           |  |  |  |  |

| RC                                          | Reference Counter                                  |  |  |  |  |

| RO                                          | Read-Only                                          |  |  |  |  |

| RTLB                                        | Reverse Translation Lookaside Buffer               |  |  |  |  |

| $\mathbf{SC}$                               | Sequential Consistency                             |  |  |  |  |

| SC for DRF                                  | Sequentially consistent for data-race-free         |  |  |  |  |

| DRF                                         | SC for DRF                                         |  |  |  |  |

| SC for DRF0                                 | Sequentially consistent for data-race-free-0       |  |  |  |  |

| DRF0                                        | SC for DRF0                                        |  |  |  |  |

| SC for DRF1                                 | Sequentially consistent for data-race-free-1       |  |  |  |  |

| DRF1                                        | SC for DRF1                                        |  |  |  |  |

| SC for DRFrlx                               | Sequentially consistent for data-race-free-relaxed |  |  |  |  |

| DRFrlx                                      | Data-race-free-relaxed                             |  |  |  |  |

| SC for HRF    | Sequentially consistent for heterogeneous- |

|---------------|--------------------------------------------|

| HRF           | SC for HRF                                 |

| SEQ           | Seqlocks                                   |

| SLM           | Sleep Mutex                                |

| SoC           | System-on-a-Chip                           |

| SPC           | Split Counter                              |

| SPM           | Spin Mutex                                 |

| SPMBO         | Spin Mutex with Backoff                    |

| SS            | Spin Semaphore                             |

| SSBO          | Spin Semaphore with Backoff                |

| $\mathbf{ST}$ | Stencil                                    |

| SyncPrims     | Synchronization Primitives                 |

| ТВ            | Thread Block                               |

| TRB           | Tree Barrier                               |

| TRBEX         | Tree Barrier with local data exchange      |

| TLB           | Translation Lookaside Buffer               |

| UTS           | Unbalanced Tree Search                     |

SC for HRF Sequentially consistent for heterogeneous-race-free

# Chapter 1 Introduction

#### 1.1 Motivation

For many years hardware designers used the increasing number of transistors provided by Moore's Law to create complex single core processors that were both faster **and** smaller than their predecessors. However, diminishing returns from optimizing single-threaded performance and the end of Dennard's scaling meant that designers could no longer design energy efficient single core processors that ran faster without consequence [11]. In response, hardware manufacturers switched from creating very fast, single core CPUs to multi-core CPUs where each core runs at a slower frequency. Although this transition allowed the hardware manufacturers to continue doubling the number of transistors on chip every two years according to the "multi-core" Moore's Law [75], subsequent work showed that multi-core scaling is limited by power constraints [58].

Heterogeneous systems with specialized compute units have emerged as one potential solution because specialization offers a natural path to energy efficiency. However, current data movement mechanisms in heterogeneous systems are very inefficient, especially for emerging applications such as graph analytics workloads and applications that use specialized memories. Additionally, heterogeneous systems are difficult to program, which makes it hard to take advantage of the benefits specialization provides. Since the memory hierarchy is expected to become a dominant consumer of overall energy [56, 86], efficient data movement is essential for efficient heterogeneous systems.

In this thesis, we redesign the memory hierarchy of heterogeneous systems. Unlike current systems, we provide performance- and energy-efficiency and programmability for emerging workloads. In particular, we focus on three key sources of inefficiency: (1) loosely coupled memory hierarchies, (2) the cache coherence protocol, and (3) the memory consistency model.

Traditional heterogeneous systems had loosely coupled memory hierarchies and required pro-

grammers to explicitly copy data between different accelerators via main memory to keep data coherent. In an effort to make heterogeneous systems more programmable, industry has recently transitioned to more tightly coupled heterogeneous systems with a unified global address space and coherent caches across CPUs and accelerators (primarily GPUs) [18, 78, 79, 135]. A global address space allows data to be transparently moved between accelerators in hardware and provides high performance for the simple, streaming, data parallel applications that heterogeneous systems traditionally run. Since these applications have little or no sharing or data reuse, heterogeneous systems use simple, software-driven coherence protocols that assume data-race-freedom, regular data accesses, and mostly coarse-grained synchronization. These protocols invalidate the entire cache at acquires and flush (writethrough) all dirty data before the next release [71]. Since synchronization (implemented with *atomics*) is infrequent, synchronization accesses bypass the private caches and are executed at the next shared level of the hierarchy.

Thus, unlike conventional multi-core CPU coherence protocols, conventional heterogeneous coherence protocols are very simple, without need for writer-initiated invalidations, ownership requests, downgrade requests, protocol state bits, or directories (Section 2.3). Further, although consistency models for heterogeneous systems have been slow to be clearly defined [13, 104, 143, 144], heterogeneous coherence protocol implementations were amenable to the familiar sequentially consistent for data-race-free (SC-for-DRF, or DRF) consistency model, such as the sequentially consistent for data-race-free-0 (SC-for-DRF0, or DRF0) model widely adopted for multi-cores today [4]. DRF0 allows programmers to reason with the familiar SC model as long as there are no data races.

Although simple heterogeneous coherence protocols work well for traditional heterogeneous applications, emerging applications with more general sharing patterns and fine-grained synchronization [38, 42, 77, 87, 121, 146] suffer because heterogeneous systems are not designed with these traits in mind. For these applications, full cache invalidates, dirty data flushes, and remote execution of synchronizations are extremely inefficient. Multi-core CPUs use hardware coherence protocols, such as MESI, to overcome this problem but prior work has observed that hardware coherence protocols are a poor fit for conventional heterogeneous applications [71, 141].

In an attempt to improve performance for these emerging applications without overly complicating the coherence protocol, recent work has introduced a new consistency model, sequentially consistent for heterogeneous-race-free (SC-for-HRF, or HRF). HRF uses scoped synchronization to associate a synchronization access with a level of the memory hierarchy where the synchronization should occur [63, 77]. For example, a synchronization access with a local scope indicates that it synchronizes only the data accessed by the threads within its own compute unit (CU, which all share the L1 cache). As a result, the synchronization can execute at the CU's L1 cache, without invalidating or flushing data to lower levels of the memory hierarchy. Thus, locally scoped synchronizations can significantly improve performance.

Although the introduction of scopes is an efficient solution to the problem of fine-grained synchronization in emerging heterogeneous applications, it increases programming complexity even further. Intrinsically scopes are a hardware-inspired mechanism that expose the memory hierarchy to the programmer. Previously, researchers had argued against such a hardware-centric view and proposed more software-centric models such as DRF0 [4]. Although DRF0 is widely adopted, it is still a source of much confusion [6]. Viewing the subtleties and complexities associated even with the so-called simplest models, we argue that GPU consistency models should not be even more complex than the CPU models. Moreover, scoped synchronization only helps when the programmer (or compiler) can identify the scope as local – if the programmer (or compiler) cannot determine this, then scoped synchronization offers no additional benefits over the traditional approach.

A second source of complexity is *relaxed atomics*, which make the DRF and HRF consistency models even more complicated. DRF0 provides high performance and programmability for many applications. However, DRF0 imposes strict constraints on all synchronization (used interchangeably with atomics) accesses. For some applications, such as graph analytics workloads, these overheads are too high and unnecessary. As a result, relaxed atomics were introduced in CPU and heterogeneous consistency models. Relaxed atomics relax the ordering constraints DRF0 imposes on all atomics to improve performance. However, relaxed atomics further increase programming complexity, because they violate the SC semantics that DRF0 and HRF provide. Consequently, it is very difficult for programmers to reason about the correctness of their code.

Moreover, relaxed atomics are extremely difficult to formalize [6, 29, 36, 37] and use correctly, so their use is strongly discouraged [36, 154]. Nevertheless, relaxed atomics are still used in modern heterogeneous systems. Relaxed atomics potentially provide significant efficiency improvements in heterogeneous systems because heterogeneous systems traditionally assume that synchronizations occur infrequently, which is not the case for emerging workloads. Consequently, the traditional approach is extremely inefficient for these workloads – which makes using relaxed atomics very attractive in heterogeneous systems.

Finally, modern heterogeneous systems also use specialized memories like scratchpads to improve efficiency. Scratchpads are software-managed and directly addressed, so they avoid the overheads the more general-purpose caches face. However, scratchpads are unaffected by the recent adoption of a unified address space, because they use disjoint, private address spaces. Specifically, scratchpads are not globally addressable or visible, so they must eagerly, explicitly transfer data between the global address space and the scratchpads' private address space, which are difficult to program for and negates some of the benefits of using scratchpads.

This state of affairs led us to ask the following questions: How can we have a global address space with simple coherence and consistency? And: can specialized memories be made part of this global address space? This work achieves these goals by adjusting the division of complexity between the coherence protocol and consistency model. First, we introduce a new coherence protocol for heterogeneous systems, DeNovo for accelerators (DeNovoA), that extends the DeNovo coherence protocol for multi-core CPUs [46, 152, 153]. DeNovoA obtains ownership for written data and uses self-invalidations to invalidate potentially stale data. Obtaining ownership for written data and synchronization variables allows DeNovoA to improve performance of applications with finegrained synchronization without the complexity of scoped synchronization. Instead, DeNovoA can use the simpler, standard DRF0 consistency model. Although DeNovoA's underlying concepts are not new, the insight that obtaining ownership for dirty data and self-invalidating valid data enables heterogeneous systems to balance efficiency and programmability is new. Next, we create a new memory consistency model, Data-Race-Free-Relaxed or DRFrlx, that extends the existing DRF consistency models to provide SC-centric semantics for all common use cases of relaxed atomics in heterogeneous systems and retains their efficiency benefits. The key insight behind DRFrlx is to focus on how programmers actually want to use relaxed atomics in real applications, instead of trying to reason about every possible use of relaxed atomics. Finally, we extend DeNovoA to integrate specialized memories into the global address space with low overhead. Here our key

insight is to use software information to create an efficient address mapping for the scratchpad in hardware. Overall, these changes makes heterogeneous systems more efficient and easier to use, especially for emerging applications like graph analytics workloads.

#### **1.2** Summary of Contributions

Overall we make the following contributions:<sup>1</sup>

Efficient Coherence and Consistency for Heterogeneous Systems: We demonstrate that DeNovoA is a viable coherence protocol for heterogeneous CPU-GPU systems, although the ideas are also applicable to other accelerators. DeNovoA is able to exploit reuse of written data and synchronization variables across synchronization boundaries without the additional complexity of scopes. The results show that DeNovoA with a DRF consistency model significantly outperforms conventional GPU coherence with a DRF consistency model across a wide range of conventional and emerging applications. After enhancing GPU coherence with HRF's scoped synchronization, DeNovoA with DRF provides much better performance for microbenchmarks with globally scoped fine-grained synchronization (on average<sup>2</sup> 21% lower execution time and 45% lower energy). For microbenchmarks with mostly locally scoped synchronization, GPU+HRF does slightly better – on average 6% lower execution time and 4% lower energy. Enhancing DeNovoA with DRF to avoid invalidating valid, read-only data at acquires reduces this performance gap and provides the same performance and energy as GPU+HRF on average. For the cases where HRF's complexity is deemed acceptable, we also develop a version of DeNovoA that uses the HRF consistency model; DeNovoA with an HRF consistency model is the best performing protocol.

Efficient Support for and Evaluation of Relaxed Atomics: We make two important contributions. First, to understand how relaxed atomics are used in heterogeneous systems, we collected examples of how developers use relaxed atomics [28, 36, 39, 63, 154] and characterized how they used relaxed atomics to identify how their use cases could be fit into an SC-centric framework. In some use cases, the existing sequentially consistent for data-race-free-1 (SC-for-DRF1, or DRF1)

$<sup>^{1}</sup>$ I did this work in collaboration with other students at UIUC. I was the lead author for the coherence and consistency [138], relaxed atomics [139] and HeteroSync [140] work. I co-led the specialized memory work [91] work with Rakesh Komuravelli. Johnathan Alsop led the stall profiling work [16]. Chapters 2 - 6 are heavily based on the publications I led and co-led.

<sup>&</sup>lt;sup>2</sup>We use arithmetic mean to represent the average throughout this thesis.

consistency model [8] can provide the same benefits as relaxed atomics without compromising SC semantics. However the remaining use cases benefit from using relaxed atomics in ways that may violate SC semantics. To handle these use cases, we propose a new consistency model, DRFrlx. DRFrlx extends DRF0 and DRF1 to provide SC-centric semantics for all common use cases of relaxed atomics in heterogeneous systems without affecting the performance benefits of relaxed atomics.

Second, we performed an evaluation to determine how beneficial relaxed atomics are in modern heterogeneous systems. In most cases the results show that DRF1 and DRFrlx provide only marginal benefit (on average, 4% execution time reduction for GPU coherence and 9% for De-NovoA). However, for two applications (BC and PageRank), DRF1 and DRFrlx's benefits were significant – depending on the input, DRFrlx reduces execution time up to 52% for DeNovoA and up to 51% for GPU coherence. The choice of coherence protocol also affects efficiency: by exploiting locality in atomic and written data, DeNovoA outperforms GPU coherence for DRF0, DRF1, and DRFrlx.

Integrating Specialized Memories Into the Unified Address Space: We introduce a new memory organization, stash, that combines the benefits of caches and scratchpads. Like a scratchpad, the stash provides compact storage and does not have overheads from indirect addressing. Like a cache, the stash is globally addressable and visible, enabling implicit and on-demand data movement and increased data reuse. We take advantage of the low overhead DeNovoA coherence protocol to efficiently integrate stash into the global address space. The results show that the stash effectively combines the benefits of scratchpads and caches. For microbenchmarks designed to exploit new use cases that the stash enables, on average, the stash reduces execution time and consumes less energy than the scratchpad, cache, and DMA configurations – 13%, 27%, and 14% lower execution time, respectively and 35%, 53%, and 32% less energy, respectively. For full-sized applications, stash improves both performance and energy: compared to the best scratchpad and cache versions, on average stash reduces execution time by 10% and 12% (max 22% and 31%), respectively, while decreasing energy by 16% and 32% (max 30% and 51%), respectively.

HeteroSync: Benchmark Suite for Fine-Grained Synchronization: We have also made several methodological contributions that underlie this thesis. First, we created a suite of microbenchmarks, HeteroSync. HeteroSync includes microbenchmarks implementing various synchronization primitives, along with annotations for locally and globally scoped atomics (Section 2.6), as well as relaxed atomics (Section 3.3).

We use the HeteroSync microbenchmarks to examine the scalability of various synchronization algorithms, coherence protocols, and memory consistency models for tightly coupled CPU-GPU systems in Chapters 2 and 3. For locally scoped microbenchmarks, DeNovoA with DRF and GPU coherence with HRF scale much better than the GPU coherence with DRF. For the hybrid and globally scoped SyncPrims, DeNovoA with DRF scales better than all other configurations. The relaxed atomics microbenchmarks show mixed scalability results: for some microbenchmarks relaxed atomics improve (strong) scalability, while for others they increase execution time, only provide small benefits, or do not impact the scalability.

Additionally, I helped develop GPU Stall Inspector (GSI), a new, detailed profiling framework that characterizes the sources of memory stalls in tightly coupled CPU-GPU systems. Unlike existing profiling tools [20, 95, 120], which do not accurately capture the subtle interactions that occur between memory requests in tightly coupled systems, GSI provides accurate profiling information about memory stalls and helps identify the bottlenecks in applications.

#### **1.3** Long-Term Impact

Modern heterogeneous systems are inefficient and hard to use. State-of-the-art heterogeneous systems use simple, software-based cache coherence protocols and complex memory consistency models like HRF. This approach can provide good efficiency, but only if the scope is local – which is often not the case in emerging applications such as graph analytics workloads. Moreover, HRF's scoped synchronization increases programming complexity. This mirrors past efforts in multi-core CPUs, which led to complicated, relaxed CPU memory consistency models. Eventually, the concurrency community adopted the DRF consistency model, but the legacy of using complex relaxed memory models still burdens DRF.

This work is the first to question whether this complexity is truly necessary, and shows that it is not. DeNovoA with a DRF consistency model effectively balances efficiency and programmability in heterogeneous systems while improving scalability and moving the complexity to the coherence protocol, where it is better hidden from the programmer. As we discuss in Chapter 2, subsequent work in industry has built on our approach – which highlights the impact of our work.

Furthermore, the current approach to coherence and consistency in heterogeneous systems makes relaxed atomics even more appealing than they are in multi-core CPUs, because they can significantly improve efficiency. However, it is very difficult to use relaxed atomics correctly, because there are no acceptable formal semantics despite more than a decade of effort.

Unlike prior work, we focus on how programmers actually use relaxed atomics in heterogeneous systems. After examining numerous use cases and applications, we found that all uses of relaxed atomics in heterogeneous systems could be grouped into five use cases. Then we designed a new consistency model, DRFrlx, that extends existing DRF consistency models and provides SC-centric semantics for these uses while retaining their efficiency benefits. Thus, DRFrlx solves a longstanding, open problem in the concurrency community and makes it easier for everyone to use relaxed atomics safely.

Heterogeneous systems also use specialized memories like scratchpads. Scratchpads often improve efficiency for specific access patterns but require programmers to explicitly move data between the global address space and the scratchpads' private address space. Thus, specialized memories like scratchpads improve efficiency but are difficult to use. Programmers could always use easierto-program caches instead, but these are often inefficient.

We introduce a new memory organization, stash, that shows how to integrate specialized memories into the unified address space while retaining their benefits. Stash combines the benefits of caches and scratchpads into a single memory organization and makes it easier for programmers to use specialized memories. As a result, programmers no longer need to choose either caches and scratchpads.

Finally, HeteroSync provides a common set of microbenchmarks that use various kinds of synchronization. Researchers can use HeteroSync to explore the differences between various finegrained synchronization algorithms, coherence protocols, and consistency models. Overall, our work creates a memory hierarchy that is more efficient and easier to program than the state-ofthe-art.

#### 1.4 Thesis Organization

This thesis is organized as follows. Chapter 2 describes the inefficient division of complexity between cache coherence protocols and memory consistency models in modern heterogeneous systems. In this chapter, we also describe the DeNovoA cache coherence protocol that we combine with a DRF memory consistency model to adjust this division of complexity and examine how the various approaches scale. Chapter 3 extends the DRF consistency model to provide better support for relaxed atomics. We analyze how relaxed atomics are used in heterogeneous systems, how they scale, and introduce DRFrlx to provide SC-centric semantics for all common uses of relaxed atomics in heterogeneous systems. In Chapter 4 we introduce the stash, and show how to extend DeNovoA to make scratchpads part of the unified global address space. In Chapter 5, we explore the scalability of the HeteroSync algorithms, coherence protocols and memory consistency models from Chapters 2 and 3. Chapter 6 qualitatively compares our work to prior work. Finally, Chapter 7 summarizes the contributions and provides some directions for future work.

### Chapter 2

### Efficient Coherence and Consistency for Heterogeneous Systems

#### 2.1 Motivation

Traditionally, heterogeneous systems, especially GPUs, focused on data-parallel, mostly streaming, applications which had little or no sharing or data reuse between CUs. Thus, GPUs used very simple, software-driven coherence protocols that assume data-race-freedom, regular data accesses, and mostly coarse-grained synchronization (typically at GPU kernel boundaries). These protocols invalidate the cache at acquires (typically the start of the kernel) and flush (writethrough) all dirty data before the next release (typically the end of the kernel) [71]. The dirty data flushes go to the next level of the memory hierarchy shared between all participating cores and CUs (e.g., a shared L2 cache). Fine-grained synchronization (implemented with *atomics*) was expected to be infrequent and executed at the next shared level of the hierarchy (i.e., bypassing private caches). We refer to this approach as *GPU-style coherence*, or *GPU coherence*.

Thus, unlike conventional multi-core CPU coherence protocols, conventional GPU-style coherence protocols are very simple, without need for writer-initiated invalidations, ownership requests, downgrade requests, protocol state bits, or directories. Further, although GPU memory consistency models have been slow to be clearly defined [13, 104, 143, 144], GPU coherence implementations were amenable to the familiar data-race-free model widely adopted for multi-cores today.

Historically GPUs have been optimized for streaming, throughput optimized applications. However, the rise of general-purpose GPU (GPGPU) computing has made using GPUs desirable for applications with more general sharing patterns and fine-grained synchronization [38, 42, 146], a trend that has been adopted by both academia and industry. Unfortunately, conventional GPUstyle coherence schemes, which perform full cache invalidations, dirty data flushes, and remote execution of synchronizations, are inefficient for these workloads. To overcome these inefficiencies, recent work has proposed associating synchronization accesses with a scope that indicates the level of the memory hierarchy where the synchronization should occur [63, 77]. For example, a synchronization access with a local scope indicates that it synchronizes only the data accessed by the CUDA thread blocks (TBs)<sup>1</sup> within its own CU (which share the L1 cache). As a result, the synchronization can execute at the CU's L1 cache, without invalidating or flushing data to lower levels of the memory hierarchy (since no other CUs are intended to synchronize through this access). For synchronizations that can be identified as having local scope, this technique can significantly improve performance by eliminating virtually all sources of synchronization overhead.

Although the introduction of scopes is an efficient solution to the problem of fine-grained GPU synchronization, it comes at the cost of programming complexity. Traditionally, GPU coherence implementations were amenable to the familiar DRF model widely adopted for multi-cores today. Unfortunately, data-race-free is not a viable memory consistency model when scopes are used since scoped synchronization accesses potentially lead to "synchronization races" that can violate sequential consistency in non-intuitive ways (even for programs deemed to be well synchronized by the data-race-free memory model). Recently, Hower et al. addressed this problem by formalizing a new memory model, heterogeneous-race-free (HRF), to handle scoped synchronization in heterogeneous systems [77]. The Heterogeneous System Architecture (HSA) Foundation [78], a consortium of several industry vendors, and OpenCL 2.0 [96] recently adopted a model similar to HRF with scoped synchronization.

Although HRF is a very well-defined model, it cannot hide the inherent complexity of using scopes. Intrinsically, scopes are a hardware-inspired mechanism that expose the memory hierarchy to the programmer. Using memory models to expose a hardware feature is consistent with the past evolution of memory models (e.g., the IBM 370 and total store order (TSO) models essentially expose hardware store buffers), but is discouraging when considering the past confusion generated by such an evolution. Previously, researchers have argued against such a hardware-centric view and proposed more software-centric models such as data-race-free [4]. Although data-race-free is widely adopted, it is still a source of much confusion [6]. Considering the subtleties and complexities associated with even the so-called simplest models, we argue that GPU consistency models should

<sup>&</sup>lt;sup>1</sup>For simplicity and without loss of generality we use NVIDIA's CUDA [118] terminology.

not be even more complex than CPU consistency models.

We show that the added complexity of scoped synchronization is not necessary. Instead, we use a coherence protocol for GPUs, DeNovoA, that is close in simplicity to conventional GPU coherence protocols, gives the performance benefits of scoped synchronization, and is amenable to using the data-race-free memory model. DeNovoA does not require writer-initiated invalidations or directories (similar to conventional GPU coherence mechanisms), but does obtain ownership for written data. By obtaining ownership, we are able to exploit reuse of written data and synchronization variables across synchronization boundaries, without the additional complexity of scopes.

Our work is the first to show that GPUs can efficiently support fine-grained synchronization at modest hardware overhead, without requiring the complexity of the HRF consistency model. Our results (Section 2.7) show that DeNovoA with DRF provides a sweet spot for performance, energy, overhead, and memory model complexity, questioning the recent move towards memory consistency models for GPUs that are more complex than those for CPUs. Moreover, by providing a low overhead, simple solution for coherence and consistency in heterogeneous systems, we enable additional work such as efficient work stealing in heterogeneous systems. Recently, a subset of the HRF authors have published a new paper that says scopes are not needed and use a coherence protocol similar in many respects to DeNovoA [15], which further demonstrates the impact of our work. We further address this and other related work in Section 6.1.2.

#### 2.2 Background

In this section we discuss the state-of-the-art in coherence and consistency for heterogeneous systems.

#### 2.2.1 GPU Coherence

In conventional GPU coherence protocols, synchronization happens infrequently and at a coarse granularity (e.g., kernel boundaries). As a result, GPUs use simple, software-driven coherence protocols that rely on data-race-freedom, invalidate the entire cache on load acquires, write-through all dirty data to the shared last level cache (LLC) on store releases, and require all synchronization accesses (performed with atomic operations) to execute at the LLC (e.g., the L2). While this scheme provides high performance for conventional GPU applications, it is sub-optimal for emerging applications with fine-grained synchronization. We provide additional details on conventional GPU coherence in Section 2.3.

#### 2.2.2 Memory Consistency Models

Depending on whether the coherence protocol uses scoped synchronization or not, we assume either DRF [4, 36, 109] or heterogeneous-race-free (HRF) [77] as the memory consistency model.

Modern memory consistency models for heterogeneous systems, like HSA, OpenCL, and HRF, are largely influenced by the decades of work on multi-core CPU memory models. Programming languages such as C, C++, and Java recently converged around the data-race-free-0 memory model which promises sequential consistency (SC) to data-race-free programs (SC-for-DRF0 or DRF0) [4, 36, 109].<sup>2</sup> The popularity of DRF0 stems from its SC-centric nature. Programmers can reason with the familiar SC model as long as there are no data races, and the absence of data races allows the system to exploit many optimizations without violating SC.

DRF0 requires programmers to distinguish between data and synchronization accesses – any access that may be involved in a race (in any SC execution) must be explicitly identified as synchronization using the atomic (for C, C++, OpenCL, HSA) or volatile (for Java) declarations. A program is data-race-free if its memory accesses are distinguished as data or synchronization, and, for all its SC executions, all pairs of conflicting data accesses are ordered by DRF0's happens-before relation. The happens-before relation is the irreflexive, transitive closure of program order and synchronization order, where the latter orders a synchronization write (release) before a synchronization read (acquire) if the write occurs before the read and the accesses conflict.

DRF0 allows the hardware and compiler to optimize data accesses, but imposes strict constraints on atomics (referred to as *SC atomics* because DRF0 requires atomics to be SC with one another). However, since atomics are relatively infrequent and data races are generally considered to be bugs [32], DRF0 provides a reasonable balance between performance and programmability.

HRF is defined similar to DRF0 except that each synchronization access has a scope attribute and HRF's synchronization order only orders synchronization accesses with the same scope. There

$<sup>^{2}</sup>$ The C, C++, and Java memory models also utilize some minor aspects of SC-for-DRF1 (DRF1). We describe DRF1 in Section 3.2.

|                 | Invalidation Initiator | Tracking up-to-date copy | Supports different scopes? |

|-----------------|------------------------|--------------------------|----------------------------|

| Conventional HW | writer                 | ownership                | yes                        |

| Software        | reader                 | writethrough             | yes                        |

| Hybrid          | reader                 | ownership                | yes                        |

Table 2.1: Classification of protocols covering conventional HW (e.g., MESI), Software (e.g., GPU), and Hybrid (e.g., DeNovoA) coherence protocols.

are two variants of HRF: HRF-Direct, which requires all threads that synchronize to use the same scope, and HRF-Indirect, which builds on HRF-Direct by providing extra support for transitive synchronization between different scopes. One key issue that this creates the prospect of synchronization races – conflicting synchronization accesses to different scopes that are not ordered by HRF's happens-before. Such races are not allowed by the model and cannot be used to order data accesses.

Common implementations of DRF0 and HRF enforce a program order requirement: an access X must complete before an access Y if X is program ordered before Y and either (1) X is an acquire and Y is a data access, (2) X is a data access and Y is a release, or (3) X and Y are both synchronization. If HRF is being used, the synchronization must use the appropriate scope. For systems with caches, the underlying coherence protocol governs the program order requirement by defining what it means for an access to complete, as discussed in the next section.

#### 2.3 A Classification of Coherence Protocols

In order to obtain a global address space with a simple coherence and consistency, one first needs to understand how coherence protocols operate. The end-goal of a coherence protocol is to ensure that a read returns the correct value from the cache. For the DRF and HRF models, this is the value from the last conflicting write as ordered by the happens-before relation for the model. Following the observations made for the DeNovo protocol for multi-core CPUs [46, 152, 153], we divide the task of a coherence protocol into the following:

(1) No stale data: A load hit in a private cache should never see stale data.

(2) Locatable up-to-date data: A load miss in a private cache(s) must know where to get the up-to-date copy.

Table 2.1 classifies three classes of cache coherence protocols in terms of how they enforce

these requirements. Modern coherence protocols accomplish the first task through invalidation operations, which may be initiated by the writer or the reader of the data. The responsibility for the second task is usually handled by the writer, which either registers its ownership (e.g., at a directory) or uses writethroughs to keep a shared cache up-to-date. The HRF consistency model adds an additional dimension of whether a protocol can be enhanced with scoped synchronization.

Although this taxonomy is by no means comprehensive, it covers the space of protocols commonly used in CPUs and GPUs as well as recent work on hybrid software-hardware protocols. We next describe example implementations from each class. Without loss of generality, we assume a two level cache hierarchy with private L1 caches and a shared last-level L2 cache. In a GPU, the private L1 caches are shared by all threads executing on the corresponding GPU CU.

#### Conventional Hardware Protocols used in CPUs

CPUs conventionally use pure hardware coherence protocols (e.g., MESI) that rely on writerinitiated invalidations and ownership tracking. They typically use a directory (or snoopy coherence if there are only a few cores) to maintain the list of (clean) sharers or the current owner of (dirty) data (at the granularity of a cache line). If a core issues a write to a line that it does not own, then it requests ownership from the directory, sending invalidations to any sharers or the previous owner of the line. For the purpose of invalidations and ownership, data and synchronization accesses (and any fences that may be required with the synchronization accesses) are typically treated uniformly. For the program order constraint described in Section 2.2.2, a write is complete when its invalidations reach all sharers or the previous owner of the line. A read completes when it returns its value and that value is globally visible.

Although such protocols have not been explored with the HRF memory model, it is possible to exploit scoped synchronization with them. However, the added benefits, are unclear. Furthermore, as discussed in Chapter 1, conventional CPU protocols are a poor fit for GPUs and are included here primarily for completeness.

#### Software Protocols used in GPUs

GPUs use simple, primarily software-based coherence mechanisms, without writer-initiated invalidations or ownership tracking. We first consider the protocols without scoped synchronization.

GPU protocols use reader-initiated invalidations. An acquire synchronization (e.g., atomic reads or kernel launches) invalidates the entire cache so future reads do not return stale values. A write results in a writethrough to a cache (or memory) shared by all the cores participating in the coherence protocol (the L2 cache with our assumptions) – for improved performance, these writethroughs are buffered and coalesced until the next release (or until the buffer is full). Thus, a (correctly synchronized) read miss can always obtain the up-to-date copy from the L2 cache.

Since GPU protocols do not have writer-initiated invalidations, ownership tracking, or (traditionally) scoped synchronization, they perform synchronization accesses at the shared L2 (more generally, the closest memory shared by all participating cores). For the program order requirement, preceding writes are now considered complete by a release when their writethroughs reach the shared L2 cache. Synchronization accesses are considered complete when they are performed at the shared L2 cache.